IBM Digital Logic Trainer. Comes in a grey wooden box with many of these pluggable modules

as you see inserted and next to the trainer. Date? 50s-60s? We need to

learn more about this unique unit! Please email us at info@smecc.org

if you can tell us any history on this! There has to be some IBM employees

that know the history behind these trainers or maybe even have the pin out

for the power supply! |

||

|

Scientific

Development Corporation Ships the |

||

|

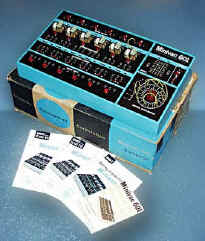

MINIVAC 601

Click on photo for larger view! |

|

|

Click on photo for larger view! |

||

|

|

||

|

|

||

|

||

|

|

||

|

DIGITAL - DEC COMPUTER LAB 1969 |

||

|

How many of us cut our teeth on these? We are interested in stories and reminiscences to post here!

APPENDIX ICOMPUTER LAB HARDWARE SPECIFICATIONS

|

||